זיילינקס משיקה את Virtex UltraScale ושוברת שיא חדש עם 4.4 מיליון שערים לוגים

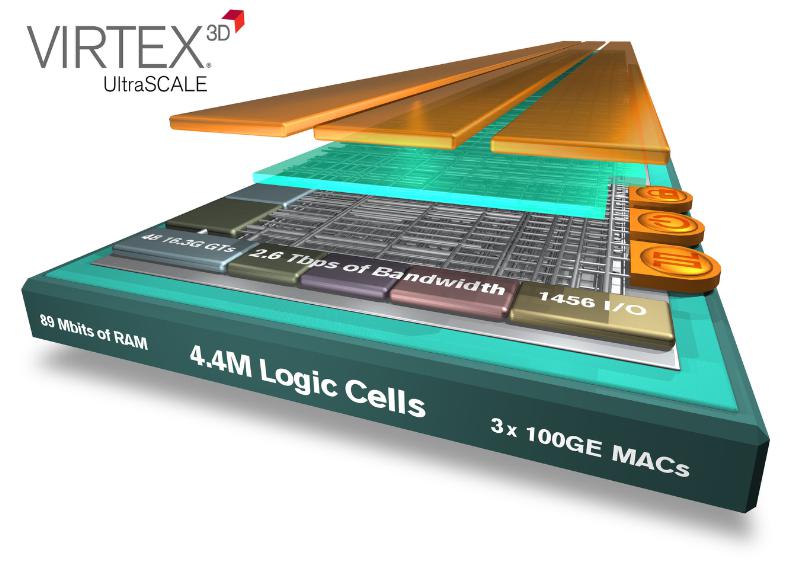

Xilinx (זיילינקס), ענקית הרכיבים המתכנתים (FPGA), הכריזה על השקת ה- Virtex UltraScaleושבירת שיא חדש בתעשייה, עם רכיב בעל 4.4 מיליון שערים לוגים (Logic Cells) נתון זה יותר ממכפיל את השיא הקודם של החברה עם רכיב Virtex®-7 2000T, שהיה עד כה בעל הקיבול הגדול ביותר בתעשייה. מדובר בהישג עקבי של שני דורות בהובלה עם מוצרי עילית מתקדמים, המוסיפים ערך ללקוח מעבר ליכולת הטכנולוגית.

רכיב ה-VU440 מרחיב את הובלת זיילינקס מפי שניים בטכנולוגית 28 ננומטר לפי ארבעה ב-20 ננומטר – ולמעשה מציע קיבול גדול יותר מאשר כל רכיב מתכנת אחר בתעשייה. באמצעות השימוש המתקדם בטכנולוגית 3D-IC (שבבי תלת-מימד), רכיב ה-VU440 מספק יותר לוגיקה בטכנולוגיית 20 ננומטר מאשר היצע המתחרים בטכנולוגית 14/16 ננומטר.

רכיב ה-Virtex UltraScale VU440 קובע קריטריון חדש בתעשייה, עם רכיב המספק 50 מיליון שערי ASIC (ASIC gates equivalent) עבור הדור הבא של אפליקציות ייצור ובנית אב טיפוס. כמו כן, רכיבי ה-20 ננומטר Virtex UltraScale מספקים את ביצועי המערכת ורוחב הפס הגבוהים ביותר, בעזרת היכולת לממש על רכיב יחיד, אפליקציות כמו 400G MuxSAR, 400G Transponder ו-400G MAC-to Interlaken bridge.

משפחת ה-Virtex UltraScale מאפשרת ללקוחות רמה חדשה של ביצועים, יכולת אינטגרצית מערכות, כמו גם רוחב פס, ויכולת נוספת של תכנות מחדש. הסקלביליות של רכיב ה-Virtex UltraScale VU440 אפשרית בעזרת ארכיטקטורה מעולם ה-ASIC (ASIC-class) – עם ניצולת עד ל-90% המאפיינת את הדור הבא של החיווט (Routing), ארכיטקטורת שעונים מעולם ה-ASIC, ניהול הספקים, יכולת למנוע צווארי בקבוק בקישוריות הפנימית וצמצום מסלולים קריטים. יכולות אלו, יחד עם שיפורים משמעותיים בארכיטקטורת בלוקי מפתח – כמו מכפלים רחבים יותר, שרשור של זכרונות מהירים, טרנסיברים בעלי יכולת של 33Gb/s, ובנוסף הקשחות IPs (Intellectual Property) של פרוטוקולים מובילים בתעשיה כמו 100Gb/s Ethernet MAC ו-150Gb/s Interlaken, מאפשרים רמות של מאות רבות של Gb/s בביצועי מערכת עם עיבוד חכם בקצב מקסימלי.

המפתח לרכיב המוביל בתעשייה ברוחב הפס ובקיבול הוא הדור השני של טכנולוגית ה- SSI (Stacked Silicon Interconnect). על סמך טכנולוגיית היצור CoWoS של TSMC, הדור הזה של טכנולוגיית ה-SSI מתאפיין בפי חמש רוחב פס בין הפיסות, וארכיטקטורת שעונים מאוחדת במעבר בין גבולות פרוסות הסיליקון וזאת על מנת לספק חווית פיתוח וירטואלית לתיכנון מונוליטי. טכנולוגיית ה-SSI של זיילינקס מאפשרת לה לספק רכיבים עם פי שניים עד פי ארבע תכולה לעומת המתחרים ובה בעת להמשיך מעבר למה שחוק מור יכול להציע. זיילינקס הציגה לראשונה את טכנולוגית ה-SSI עם רכיבי Virtex®-7 2000T בשנת 2011 – הרכיב הגדול בעולם באותו הזמן – הבנוי מ-6.8 מיליארד טרנזיסטורים, שאפשר ללקוחות גישה חסרת תקדים לשני מיליון שערים לוגים (Logic Cells) שהם שווי ערך ל-20 מיליון שערי ASIC.

רכיבי Xilinx UltraScale מאפשרים יתרונות מעולם ה-ASIC עם ארכיטקטורת ASIC מתכנתת היחידה בתעשייה המאפשרת מעבר בין טכנולוגיית 20 נונמטר Planar לטכנולוגית 16 ננומטר FinFET ומרכיבים מונוליטים דרך 3D-IC. דרך שילוב המובילות הטכנולוגית של TSMC עם חבילת הפיתוח Vivado®, שיש לה חוזקות פיתוח של סביבת ASIC, ביחד עם מתודולוגיית התכנון UltraFast™, זיילינקס נמצאת שנה אחת או שתיים קדימה, ביכולת לספק מימוש של פי 1.5 עד 2 בביצועי המערכת ויכולות האינטגרציה.

רכיבי Virtex UltraScale יהיו זמינים ללקוחות במחצית השניה של 2014.